2016 – 2017 Meeting Reports

Military Application of Electromagnetic Environmental Effects

Wednesday November 15th, 2017

Kris Hatashita, Consultant to the Canadian Department of National Defence

Our final meeting of 2017 was held at Compliance Testing Labs in Mesa Arizona on Wednesday, November 15th, in conjunction with the IEEE EMCS Board of Directors meeting in downtown Phoenix that previous weekend.

The evening began at 5:30 pm with the customary social hour and excellent Mexican food catered by the chapter.

The meeting itself began a little before 7 pm, with Glen (our chapter chair) discussing chapter business. Glen talked about the upcoming 2018 IEEE EMC Symposium in Long Beach, our Chapter’s corporate sponsorship program and new developments on our Chapter website. He then introduced Vignesh Rajamani who is both a member of the Phoenix Chapter as well as the Vice President of Member Services with the EMC Society. Vignesh communicated the benefits of IEEE EMC Society membership, including the vast technical resources and the obvious networking and career benefits. Vignesh then introduced Frank Sabath, the EMCS president.

Frank gave our chapter a brief run-down on Society activities, including plans for a Journal of EMC best practices, which is anticipated to become available mid next year. Be on the lookout for a call for papers for the Journal. There are also plans to start a “technician’s corner” in the EMCS magazine to provide more ‘hands on’ information to our members.

Frank then returned the floor to Glen, who began the usual around-the-room introductions, including the companies that are hiring and individuals looking for work. There are several companies looking for experienced EMI personnel in the Phoenix area!

Glen then introduced our featured speaker, Kris Hatashita – a Consultant to the Canadian Department of National Defense.

Kris had to ‘opportunity’ to do EMC work in Afghanistan in 2007 in a real war-zone environment. He mentioned that the Canadian army doctrine similar to the US army – all equipment has to be effective, self-compatible, compatible to the EM environment, safe to operators and must not emit compromising emissions. In a military environment, EMC is always serious/mission critical. Frequency Coordination must be done considering local communications, coalition level communications, intentional jamming, and with regard to hostile intentions to bring down communications systems.

Kris cited a prime EMC example involving a ground vehicle that was being deployed in Kandahar whose communications range was only about 10 miles! He took the vehicle to a remote location in Canada with an approximately 90 km long straight flat road. The vehicle got to a 55 km range before communications was lost. Then, the vehicle operator was instructed to turn on subsystems. When the IR target acquisition was turned on, it completely buried the communications. It turned out that the coax cable leading to the communications system was routed through two pins through a MIL-circular connector, completely violating its shielding integrity!

A further cause of concern for communications on the vehicle was the microphone/headset. It turned out that soldiers had modified the headset by wiring-in an audio jack for their iPhone, also violating shielding!

Kris mentioned that weapons systems are getting more complex and integrated. Consider the example of the Integrated Soldier System, where IR sensors, short/long range communications, UAV controls, and sensors are all collocated on a single soldier. The remedy to these complex EMC problems is to use MIL-STD-461!

Kris showed a standard MIL_STD-461 RS03 setup, which tests Army ground equipment to 50 V/m. A significant field strength indeed.

Nuclear Electromagnetic pulse or NEMP exhibits extremely fast transients with very high levels of magnetic and electric fields. Typical field levels can be 50 kV/m, 100 A/m2 and 6.6 Mw/sq2. While low altitude nuclear events emit a sizeable EMP out to about 50 km, high altitude events can emit sizeable levels on a continental scale – at almost 2000 km distance. In this region, a high percentage of equipment will cease to function. The power grid will be overridden – possibly irreparably. 8-10 nuclear weapons could foreseeably take out electronics globally. In the military world, every device is designed to withstand a certain level of EMP.

Kris then described radiation hazards (RADHAZ) examples. One was a personnel radiation hazard, where an ARV vehicle went straight to Afghanistan due to operations requirements without EMC testing beforehand. This vehicle had a high-power counter-IED jamming transmitter. Soldiers complained about blurred vision, ringing in ears and sinus problems. Measurements showed that the soldiers were in a 450 V/m field! This is about 4-6 times the permitted levels. The solution was to reduce the RF power and to reduced soldiers time allowed in the EM field.

Kris then spoke about high energy radiation on ordnance or HERO. He showed video of the infamous USS Forrestal incident in 1967. Now ordnance has its own set of high field strength radiated test limits.

Finally, Kris talked about EM Security – TEMPEST and showed a very interesting example of coupling between two LCD monitors.

Kris closed his presentation by stating that EM spectrum is one of 4 new battle grounds introduced in the 20th century: Air, Space, Internet and the EM spectrum. It is interesting to note that the EM spectrum is common to all battlegrounds.

After the talk, Glen Gassaway thanked Kris for his fine presentation! The meeting was closed at 8:30.

We are grateful to Compliance Labs in Mesa AZ for hosting and providing their facilities for this event.

The 2017 Phoenix EMC Symposium

Meeting notes Published by Janet O’Neil (ETS-Lindgren)

The Phoenix EMC Chapter held a one-day regional symposium on Wednesday, April 26 at the Embassy Suites Hotel in Tempe, Arizona. The impressive line up of speakers and topics included:

- EMC Design Review by Daryl Gerke of Kimmel Gerke and Associates

- Smart Antennas: Technoogy Integrating Antennas, DSP, Communications and Networks by Constantine Balanis, Regent’s Professor, Department of Electrical Engineering, Arizona State University

- Wireless Integration Interference Challenges By Harry Skinner, Director and Senior Principal Engineer, Intel Labs

- Understanding Device Performance in a Crowded RF Environment: An Overview of ANSI C63.27 and Coexistence Testing By Dr. William Young, Group Leader, Shared Spectrum Metrology, NIST

- Anechoic Absorber Consideration in the W Band and Absorbers Under High Power Incident Field By Zhong Chen, Director of RF Engineering, ETS-Lindgren

- The Internet of Things – Wireless Technologies & Utilization by Vignesh Rajamani, Senior Associate, Technology Development and Practice, Exponent and Mark Goldstein, President, International Research Center

Mr. Daryl Gerke that explained like vaccinations for children, an EMC design review can prevent serious problems later, such as a failed EMC test, or worse, a failed product in the field. This talk addressed ten EMC concerns at both the schematic and board construction levels. Daryl shared the methodology he has used for many years in his EMC consulting practice. As Daryl likes to say, “An ounce of prevention can be worth a pound of shielding.”

Professor Balanis, the keynote speaker, noted as the demand for mobile communications is constantly increasing, the need for improved capacity, greater coverage and higher transmission quality rises. Therefore, a more efficient use of the radio spectrum is required. Smart antenna systems are capable of efficiently utilizing the radio spectrum, and they are a promise for an effective solution to meet the desired performance demands in network and communication systems. Smart antenna technology has been considered for mobile platforms such as automobiles, cellular phones (mobile units), and laptops. Smart antennas integrate many technologies, including antennas, digital signal processing, communications and networks. The advancement and integration of the characteristics of each of these areas is critical to the efficiency and performance of a communication system channel, as measured by Bit-Error-Rate (BER) and network Throughput. This presentation reviewed the basic principles of smart antennas. It also presented and compared the BER and throughput of different antenna array geometries, such as the uniform rectangular array (URA).

Dr. Bill Young of NIST advised with an abundance of wireless devices saturating daily life, the ability of devices to coexist among other devices is of increasing interest. Ideally, a manufacturer would like to understand how their wireless device would perform in a crowded spectrum environment (e.g., the 2.4 GHz ISM band). However, this question is often one that eludes traditional EMC testing which by design excludes the frequency bands where a device intends to communicate. Unlike traditional EMC testing, coexistence testing intentionally focuses on the band(s) in which the device under test uses for wireless communications. This presentation examined the fundamental goals of coexistence testing, methods for quantifying coexistence, and the new ANSI C63.27 standard for evaluating wireless coexistence. This standard outlines four coexistence measurement methods and provides some technology specific guidance for common scenarios (e.g., Wi-Fi and Bluetooth). Despite the release of the standard, many challenges related to coexistence metrology remain. These challenges were discussed along with some of the intricacies of coexistence testing for medical devices.

Mr. Harry Skinner of Intel emphasized the fact that wireless communication on everything is fast becoming the norm. Unfortunately, adding wireless functionality to devices has its own challenges. One of those challenges is the close proximity of intentional wireless transceivers with high-speed digital circuitry. This talk introduced broad concepts related to what is widely known as radio frequency interference. Topics presented included both platform and RF communications based interference sources and victims. It covered foundational aspects related to differences between unintentional and intentional radiators including coexistence challenges. As well as addressing current challenges and possible solution paths, the talk also looked ahead at potential challenges related to future communications standards and devices.

Mr. Zhong Chen of ETS-Lindgren gave a two-part presentation. The first presentation was on the absorber considerations for W-band (75 GHz – 110 GHz). He noted that the absorber performance data is typically only available only to 40 GHz, and higher frequency data is often extrapolated. This presentation showed the actual measured reflectivities of common microwave absorbers in the W band. It showed that the extrapolated data from lower frequencies might not be accurate. Zhong also showed how paint on the absorber surface might affect the absorber reflectivity, and if black-tip (leaving the tip of the absorbers unpainted) is an effective technique. The second part of his presentation dealt with the power handling of the absorbers, and provided analyses on the thermal behavior of the absorbers under high electromagnetic incident field. Data was presented on internal and surface temperatures of typical absorbers under varying field strength, and some mitigating factors to lowering the temperatures were discussed.

The last presentation of the day was by the tag team of Dr. Vignesh Rajamani of Exponent and Mark Goldstein of the International Research Center. They explained that the next internet wave, the Internet of Things (IoT), would connect tens of billions of new sensors and devices in the coming years driving sustainability while transforming home, business, government, industrial, medical, transportation, and other complex ecosystems. The presentation examined IoT’s evolving wireless protocols, their pro and cons, and deployment trends and prospects including the impact of 5G. It also explored how IoT will be implemented and monetized across various application spaces, creating new business models from pervasive sensor deployments and data gathering, accompanied by new privacy and security risks, as well as roadblocks and operational challenges, emerging standards and protocols, gateways and ecosystem integration, big data strategies, and analytic opportunities.

Intermixed with this fascinating technical program was an exhibition of the latest in EMC products and services. The attendees who visited with the exhibitors present during the breaks, lunch and the reception with the speakers following the last presentation appreciated the over 20 tabletop displays. Several raffle prizes provided an exciting end to a great day of education and networking.

The Phoenix EMC Chapter Officers and event organizers wish to thank the fantastic speakers for the excellent presentations, the lunch sponsors Advanced Test Equipment Rentals, Ametek CTS US, AR RF/Microwave Instrumentation and Curtis Industries/Tri-Mag, the reception sponsor Fischer Custom Communications, and all the exhibitors and attendees who made the Phoenix EMC Symposium a big success! Over 80 people attended this event – that encouraged Phoenix EMC Chair, Glen Gassaway of Southwest EMI Consulting, to start thinking about planning the next Phoenix EMC Symposium in 2019!

The Phoenix EMC Chapter held a regional symposium on April 26, 2017 at the Embassy Suites Hotel in Tempe, Arizona. Over 80 people attended the full day technical program and exhibition.

Thursday, November 10, 2016

| Speaker: Bruce Archambeault, PhD

IBM, Raleigh NC www.brucearch.com Location: Compliance Testing, LLC |

(See all event photos here.) — all photos by Steve Schafer of Compliance Testing Lab in Mesa

Facts about Decoupling Capacitors and PCBs!

Our final meeting of 2016 was held on November 11th 2016 at Compliance Testing Labs in Mesa Arizona, in conjunction with the IEEE EMCS officer’s meeting in downtown Phoenix that weekend.

The evening began with the customary social hour and some mighty fine pulled pork, smoked chicken, beans, and coleslaw from Tom’s BBQ in Mesa.

The meeting began with some announcements from our chapter chairman, Glen Gassaway. He went over IEEE business, updates regarding our new website (including our new corporate sponsorship program) and the newly created job board. Glen also talked about our upcoming IEEE Phoenix Mini-Symposium coming up in April. We then had the usual around the room introductions and who is hiring and who is looking for work.

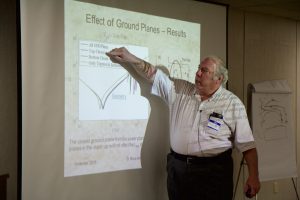

Our speaker, Dr. Bruce Archambeault had prepared a lecture on “Facts about Decoupling Caps and PCB’s”. His presentation covered case studies for different effects of capacitance value, number of capacitors, capacitor density, and capacitor configuration. Multiple analyses showed the different effects of ground plane geometries.

Bruce spoke about the physical cause of inductance (current path), and identified each portion of overall path. He mentioned that the value of capacitance is not as important as the number of capacitors, as well as the series inductances of the traces and vias leading to the capacitors. Significantly, the via connection configuration can dramatically influence inductance. If power/ground-reference planes are deep in PCB stackup, capacitor placement has less impact than might be expected.

Design conclusions include keeping the PWR/GND plane pair close to IC minimizes LIC. Keeping capacitors close to the power layer minimize the inductance Ldecap from the capacitor to the power plane. The PWR/GND plane separation shall be as small as possible. Placing caps under the IC can benefit the design if board is thin or the plane inductance is large. Also, the ground plane closest to the power layer affects the response most, all other ground layers have very little influence.

Dr. Archambeault was kind enough to give us a copy of his presentation. His final note was “A ring is a current loop which creates inductance and is the root of all evil! After the talk, Glen Gassaway gave Bruce a custom Arizona coffee mug for his fine presentation!

We thank Compliance Labs for hosting and providing their facilities for this event.

(See all event photos here.)

Thursday, August 25, 2016

PRACTITIONERS APPROACH TO EMC TESTING WITH REVERBERATION CHAMBERS

|

With Dr. Vignesh Rajamani

Senior Associate Technology Development and Practice Exponent, Inc.

Location: Exponent, Inc. Phoenix, Arizona 85027 |

(See all event photos here.)

The IEEE EMC Phoenix Chapter held a very interesting and well-attended meeting on Thursday, August 25th 2016 at Exponent Inc, located at 23445 N 19th Avenue in Phoenix.

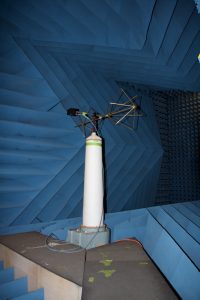

The meeting began with a terrific tour of the Exponent facility. The ‘official’ Exponent tour guide (Dan Kingsley) gave us a great overview of what Exponent does – especially given the short time we had. We were able to view their crash test facilities (indoor and outdoor), their motion capture facility, the engineering lab, their anechoic chamber and their newly-constructed reverberation chamber. We even took a group picture around one of the ‘crashed’ vehicles!

We then held our customary round table introductions and the call for EMC employment/employers. Many of us were able to talk about what interesting activities they have been up to since the last meeting.

|

After the general chapter business was completed, we were given a nice introduction of Exponent’s capabilities by John Pye, the Practice Director at Exponent. It’s amazing how many interesting ‘cases’ that Exponent is involved with! |

After John’s presentation, our primary speaker Dr. Vignesh Rajamani took the stage. First, he answered the basic question: What is a Reverberation Chamber (RC)? He compared them to Anechoic Chambers with a list of pros and cons for each. We were shown several existing RCs – all the way from table mounted shielded boxes to truck-sized mega-chambers.

Dr. Rajamani spoke at length about various tuner designs and mode-stirring versus mode-tuning methodologies. He mentioned that there are significant advantages over an anechoic chamber for both emissions and susceptibility testing – especially in terms of repeatability and in cases where high field strengths are needed. Another argument for the use of an RC is in situations where the EUT is quite large and complex; as all aspect angles may be observed as opposed to ‘more-horizontal’ angles observed in typical anechoic or OATS testing.

Dr. Rajamani then discussed four specific applications where an RC should be considered: a) Shielding effectiveness measurements, b) Simulation of a complex radio environment (as in wireless device testing), c) Measurement of antenna efficiency and d) Characterizing below deck and aircraft cockpit EM environments.

Dr Rajamani was kind enough to distribute a copy of his presentation, here.![]()

After Dr. Rajamani’s presentation, Glen Gassaway presented him with an “Arizona Thermometer’, which includes an artist’s rendition of a skeleton leaning against a cactus. Welcome to Arizona, Vignesh!

The meeting was called to a close at about 8:15 pm. Our Chapter thanks Exponent and Dr. Rajamani for as very fine and interesting evening – and thanks to all who attended!

Speaker Biography:

Dr. Rajamani is an expert in the electromagnetic characterization and application of reverberation chambers and holds a position of Senior Associate at Exponent. A main thrust of his research and project experience in the area of reverberation chambers has been towards increasing test accuracy. His expertise includes statistical electromagnetics, validation and optimization techniques for computational electromagnetics, communication system test in complex multipath environments, EMI/C Issues with Unmanned Aerial Systems, antenna systems and radio frequency (RF) design, and estimation probability of failure of electronic systems due to electromagnetic interference and compatibility.

Dr. Rajamani is the Vice President of Member Services for the IEEE Electromagnetic Compatibility (EMC) Society and involved with several technical committees and educational activities through the EMC Society. He is a Senior Member of IEEE and served as a distinguished lecturer for the IEEE EMC Society for term 2013-2014. He has lectured around the world on reverberation chamber test methodologies and has taught design engineering seminars for faculty and students at many universities focusing on challenges in engineering education and prepare the faculty to handle them by spreading a significant number of Project Based Learning (PBL) classes across the curriculum. Prior to joining Exponent, Dr. Rajamani was with Oklahoma State University as a Visiting Assistant Professor where he taught courses in engineering design and performed research in probability of failure of electronic systems in harsh electromagnetic environments.

About Exponent

“Exponent is a multi-disciplinary engineering and scientific consulting firm that brings together more than 90 different disciplines to solve important engineering, science, regulatory, and business issues. For nearly 50 years [they] have provided engineering, scientific, environmental and health consulting services to corporations, insurance carriers, government agencies, law firms and individuals. Its Phoenix Test and Engineering Center is home to unique test and design analysis services from vehicle crash testing to development of ground penetrating radar systems and robots used in military applications.” Exponent can be thought of as the ‘real’ myth-busters! Exponent has been involved in the investigations of many well-known incidents including the Toyota sudden unintended acceleration, the September 11 attacks in New York, and the Deepwater Horizon investigation.

See all event photos here.

For earlier meetings, see our Older Meetings Archive page, here.